## **NANO**

2008 Vol. 8, No. 3 876-880

## An Organic/Si Nanowire Hybrid Field **Configurable Transistor**

Qianxi Lai,† Zhiyong Li,‡ Lei Zhang,† Xuema Li,‡ William F. Stickle,§ Zuhua Zhu,† Zhen Gu,† Theodore I. Kamins,‡ R. Stanley Williams,‡ and Yong Chen\*,†

Department of Mechanical and Aerospace Engineering and California NanoSystems Institute, University of California, Los Angeles, California 90095, Quantum Science Research, Hewlett-Packard Laboratories, 1501 Page Mill Road, Palo Alto, California 94304, and Advanced Materials Process Lab and Advanced Diagnostic Lab, Hewlett-Packard Company, Corvallis, Oregon 97330

Received November 29, 2007; Revised Manuscript Received January 16, 2008

## **ABSTRACT**

We report a field configurable transistor (FCT) fabricated on a Si nanowire FET platform by integrating a thin film of conjugated polymer poly[2-methoxy-5-(2'-ethylhexyloxy)-p-phenylene vinylene] (MEH-PPV) and an ionic conductive layer (RbAg<sub>4</sub>I<sub>5</sub>) into the gate. The FCT can be precisely configured to desired nonvolatile analog state dynamically, repeatedly, and reversibly by controlling the concentration of iodide ions in the MEH-PPV layer with a gate voltage. The flexible configurability and plasticity of the FCT could facilitate field-programmable circuits for defect-tolerance and synapse-like devices for learning.

The continued miniaturization of the Si-based field-effect transistor (FET) will reach its fundamental physical limit in a decade or so, which has led to significant efforts in the development of new nanoscale electronic devices based on Si nanowires,<sup>2</sup> carbon nanotubes,<sup>3</sup> molecules,<sup>4</sup> etc. Simple electronic circuits based on these nanodevices<sup>5–7</sup> have also been demonstrated, but it is challenging to integrate these devices into large-scale functional circuits for practical applications due to the inevitable defects introduced during the fabrication of these devices and circuits. Various defecttolerant circuit architectures have been proposed, 8-11 in which the defects in circuits can be identified by postfabrication tests, and then the defects can be corrected and the circuits can be reconfigured toward desired functions. To build up the defect-tolerant circuit, it is highly desirable to develop nanoscale field configurable devices that can not only preserve the merits of the Si FET but also incorporate synapse-like analog configurability and plasticity. Floating gate Si FETs have been used for digital field programmable circuits, but such devices can hardly be integrated with nanowire-based devices and are difficult to configure precisely to a desired analog state. 12 Recently, organic molecules were incorporated into the gate structures of Si FETs<sup>13</sup> and semiconductor nanowire transistors, 14,15 which can then be configured to bistable or multiple discrete electronic states by applying a gate voltage to control the redox state of the

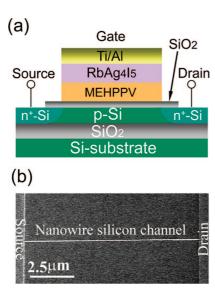

cm<sup>3</sup> and has a width of 80 nm, a thickness of 60 nm, and a length of 10  $\mu$ m, respectively. A scanning electron microscope (SEM) image shows its structure in Figure 1b. The n-Si source and drain had a nominal phosphorus doping concentration of  $1 \times 10^{20}$ /cm<sup>3</sup>. The source and drain patterns were fabricated by photolithography, and the nanoscale Si channel was fabricated by e-beam lithography on a Si layer

molecules. Although these devices have been demonstrated

for multiple-state nonvolatile memory and programmable

logic applications, it is difficult to integrate a liquid

electrolyte into a gate structure or semiconductor nanowires

In this letter, we report an organic/Si hybrid field-

configurable transistor (FCT) fabricated on a Si nanowire

FET platform that can be flexibly configured to precise

analog states. The device structure is shown schematically

in Figure 1a. A thin film of poly[2-methoxy-5-(2'-ethyl-

hexyloxy)-p-phenylene vinylene] (MEH-PPV), a conjugated

polymer, and an inorganic layer of RbAg<sub>4</sub>I<sub>5</sub>, an ionic

conductor, 16 were sandwiched between the gate SiO<sub>2</sub> layer

and an Al/Ti metal gate electrode to incorporate the config-

uration function. When a gate voltage exceeding a threshold

value is applied, depending on its polarity, the iodide ions

from the RbAg<sub>4</sub>I<sub>5</sub> are injected into or extracted from the

MEH-PPV layer, resulting in the configuration of the FCT

electronic characteristics.

with back gates into more general-purpose circuits.

The FCT preserves the conventional Si source-channeldrain (n-p-n) structure. The FET Si nanowire channel is p-Si with a nominal boron doping concentration of  $3 \times 10^{17}$ /

<sup>\*</sup> Corresponding author. E-mail: yongchen@seas.ucla.edu.

<sup>†</sup> University of California, Los Angeles.

<sup>#</sup> Hewlett-Packard Laboratories.

<sup>§</sup> Hewlett-Packard Company.

**Figure 1.** (a) Schematic showing the structure of a polymer/Si nanowire hybrid field-configurable transistor. (b) SEM image showing the SOI-based Si nanowire channel region.

on a silicon-on-insulator (SOI) wafer. A 3 nm thick gate SiO<sub>2</sub> insulating layer was prepared by thermal oxidation to cover the Si nanowire channel. A layer of MEH-PPV with a thickness of 60 nm was spin-coated on top of the SiO<sub>2</sub> insulating layer. A 60 nm thick RbAg<sub>4</sub>I<sub>5</sub> ionic conducting layer was deposited on the top of the MEH-PPV polymer layer by thermal evaporation of a powder mixture of 82 mol % AgI and 18 mol % RbI. Finally, a metal gate electrode consisting of a 20 nm thick Ti layer followed by an 80 nm thick Al layer was deposited by electron-beam evaporation. The MEH-PPV polymer beyond the gate electrode area was etched away with an O<sub>2</sub> plasma using the gate metal electrode as an etching mask. Conventional Si FETs (without the RbAg<sub>4</sub>I<sub>5</sub>/MEH-PPV bilayer in the FCT gate shown in Figure 1a) were also fabricated as control devices by using the same process as described above, except that the steps to integrate the RbAg<sub>4</sub>I<sub>5</sub>/MEH-PPV bilayer were omitted. The test results of the control FETs demonstrated decent transistor characteristics, which are included in the Supporting Information.

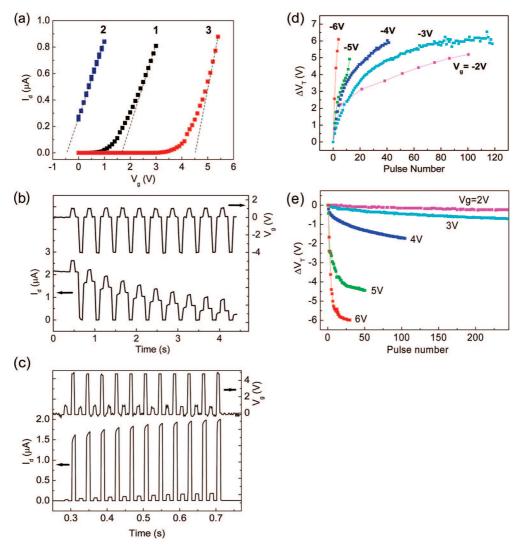

All FCTs were measured at room temperature under vacuum ( $<10^{-4}$  Torr) in a Desert Cryogenics vacuum probe station to prevent oxygen and moisture from contaminating the ionic/organic bilayer. The electrical measurements of the FCT and the control FET devices were carried out using a HP4156B semiconductor parameter analyzer, an Agilent 31220 wave function generator, and a Fluke 199B oscilloscope. Typical source—drain current (I<sub>d</sub>) versus gate—source voltage  $(V_g)$  characteristics of the FCTs with a drain—source voltage  $V_d = 1 \text{ V}$  and a grounded source are shown in Figure 2a for different configuration states. Curve 1 in Figure 2a shows an  $I_d$ - $V_g$  characteristic for a FCT in its initial state with a threshold voltage  $V_T \approx 1.0 \text{ V}$ . After sweeping a large positive configuration voltage  $V_g$  from  $0 \rightarrow 7$  V within 3.5 s, the threshold voltage changes to  $V_{\rm T} = -1.0$  V (curve 2); after sweeping a negative configuration voltage  $V_{\rm g}$  from 0  $\rightarrow$  -5 V,  $V_{\rm T}$  = 4.0 V (curve 3). The ratio of  $I_{\rm d}$  for a FCT measured at state 2 ( $V_T = -1.0 \text{ V}$ ) to that measured at state 3 ( $V_{\rm T}=4.0~{\rm V}$ ) was more than  $10^6$  when tested at  $V_{\rm g}=0.5~{\rm V}$  and  $V_{\rm d}=1~{\rm V}$ . More than 30 FCTs have been fabricated and tested separately. Before configuration, the original threshold voltages of the as-fabricated FCTs were distributed between 1 and 2 V. After sweeping a configuration voltage  $V_{\rm g}$  from  $0 \rightarrow 7~{\rm V}$  or  $0 \rightarrow -5~{\rm V}$ , the threshold voltages of the FCTs were configured to  $-1.0 \pm 0.2~{\rm V}$  and  $4.0 \pm 0.2~{\rm V}$ , respectively. The wide configuration range of the gate threshold voltages ( $-1.0~{\rm to}~4.0~{\rm V}$ ) and the large configuration ratio of the source—drain currents (up to  $10^6$ ) provides the flexibility to configure FCTs to a wide range of desired characteristics in a field configurable circuit. After configuration, the  $V_{\rm T}$  remained stable for a long retention time when it was tested with  $|V_{\rm g}-(V_{\rm d}+V_{\rm s})/2|<1.5~{\rm V}$ , as discussed below.

The FCTs can be configured to arbitrary states dynamically and reversibly by applying a series of  $V_{\rm g}$  pulses with different amplitude, polarity, and duration. A series of negative configuration  $V_{\rm g}$  pulses with a fixed amplitude  $V_{\rm g}=-4~{\rm V}$ and a duration of 100 ms was applied to the FCT. After each pulse, the FCT was stabilized at  $V_g = 0$  V for 100 ms, and then  $I_d$  was measured at  $V_g = 1$  V and  $V_d = 1$  V. As shown in Figure 2b, I<sub>d</sub> was progressively decreased by the negative configuration  $V_{\rm g}$  pulses. When a series of positive configuration  $V_g$  pulses with an amplitude  $V_g$ = 5 V and a duration of 10 ms was applied, the process described above was reversed. After each pulse, the FCT was stabilized at  $V_{\rm g} =$ 0 V for 10 ms, and then  $I_d$  was measured at  $V_g = 1$  V and  $V_{\rm d}=1$  V. As shown in Figure 2c,  $I_{\rm d}$  was progressively increased by the positive configuration  $V_{\rm g}$  pulses. The results indicate that the FCT can be gradually tuned by low amplitude configuration voltages that are compatible with CMOS circuits.

The configuration rate of the FCT can be modified by the amplitude of the configuration gate voltages. To study this effect,  $V_{\rm T}$  in a FCT was first configured to its minimum value by applying a positive configuration voltage  $V_{\rm g} = 7$  V with extensive duration, and then  $I_d$  was sequentially decreased by a series of  $V_{\rm g}$  pulses with a fixed duration of 100 ms and fixed amplitudes of -6, -5, -4, -3, and -2 V, respectively. The change of the FCT threshold voltage  $\Delta V_{\rm T}$  was derived from the change of  $I_d$  and is shown in Figure 2d as a function of the number  $N_p$  of the applied  $V_g$  pulses. The configuration rate,  $d\Delta V_T/dN_p$ , increased significantly when the amplitude of  $V_{\rm g}$  pulses increased from -2 to -6 V. In a similar fashion,  $V_{\rm T}$  in a FCT was first configured to its maximum value by applying a negative configuration voltage  $V_g = -6$  V with extensive duration and then  $I_d$  was sequentially increased by a series of  $V_{\rm g}$  pulses with a fixed duration of 100 ms and fixed amplitudes of 2, 3, 4, 5, and 6 V, respectively. The change of the FCT threshold voltage  $\Delta V_{\rm T}$  was derived from the change of  $I_d$  and is shown in Figure 2e as a function of the number  $N_p$  of the applied  $V_g$  pulses. The configuration rate,  $d\Delta V_T/dN_p$ , increased significantly when the  $V_g$  pulse increased from 2 to 6 V.

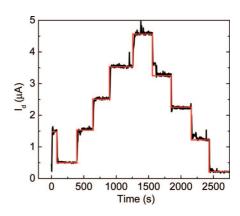

The FCT can be dynamically configured to a targeted state precisely by a closed-loop feedback control circuit (the details of the circuits are described in the Supporting Information).

Figure 2. (a)  $I_d - V_g$  data (symbols) measured for the initial state before configuration (curve 1), after sweeping  $V_g$  from  $0 \rightarrow 7$  V (curve 2), and after sweeping  $V_g$  from  $0 \rightarrow -5$  V (curve 3). The intercept with the  $V_g$  axis of the dashed straight line tangent to the  $I_d - V_g$  data points determines the transistor threshold voltages  $(V_T + (V_d + V_s)/2)$  for each configured state. (b)  $I_d$  (lower curve) is progressively decreased by applying a series of negative configuration  $V_g$  pulses with an amplitude  $V_g = -4$  V (upper curve). (c)  $I_d$  (lower curve) is progressively increased by applying a series of positive configuration  $V_g$  pulses with an amplitude  $V_g = 5$  V (upper curve). (d) The change of the threshold voltage  $V_T$  is plotted (data points) as a function of the number of negative configuration gate voltage pulses,  $N_p$ , for fixed amplitudes  $V_g = -6$  V (red), -5 V (green), -4 V (deep blue), -3 V (sky blue), and -2 V (magenta). (e) The change of the threshold voltage  $V_T$  is plotted (data points) as a function of the number of positive configuration gate voltage pulses,  $N_p$ , for fixed amplitudes  $V_g = 6$  V (red), 5 V (green), 4 V (deep blue), 3 V (sky blue), and 2 V (magenta).

During the configuration,  $I_d$  was measured and compared continuously with a target reference current  $I_{ref}$ , which was preset by the training circuit. If  $I_d$  was higher or lower than  $I_{\rm ref}$ , negative or positive  $V_{\rm g}$  pulses, respectively, were applied to the FCT to reduce the difference,  $I_{\rm d}-I_{\rm ref}$  l. The  $V_{\rm g}$  pulses were kept at a fixed duration of  $10 \mu s$  and a fixed amplitude of  $V_g = 8.5 \text{ V}$  when  $I_d < I_{ref}$  or -5.5 V when  $I_d > I_{ref}$ , but the number of applied  $V_{\rm g}$  pulses was set by the training circuit to be linearly proportional to  $I_{\rm d}-I_{\rm ref}$  to adjust the configuration rate automatically. The reading, comparison, and configuration occurred continuously and simultaneously. The high-frequency transient currents induced by the configuration  $V_{\rm g}$  pulses were filtered out. As shown in Figure 3,  $I_{\rm ref}$  was set to different values in the range 0.25–4.5  $\mu$ A, and  $I_{\rm d}$  was automatically configured to follow the change of  $I_{\rm ref}$ by applying the configuration  $V_{\rm g}$  pulses. The configuration

**Figure 3.** Source—drain current,  $I_{\rm d}$  (black line) is automatically configured by a closed-loop feedback control circuit to various target reference currents,  $I_{\rm ref}$ , (red line), shown as a function of time.

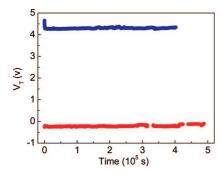

**Figure 4.** Fluctuation of gate threshold voltages,  $V_{\rm T}$ , is shown as a function of time after a field-configurable transistor was configured to a low (red symbols) and a high (blue symbols)  $V_{\rm T}$  value, respectively.

process was halted after  $I_{\rm d}$  reached the preset  $I_{\rm ref}$  value, and the device remained in the configured state until  $I_{\rm ref}$  was reset to a different value to initiate another configuration cycle. The targeted configuration was carried out on three randomly selected FCTs, all of which were successfully configured to the targeted multiple states.

The nonvolatility of FCT devices was examined by monitoring the retention time of the configured FCT states. The FCTs were first configured to a high or low  $V_T$  state, then  $I_d$  was measured every 10 s for five days with low testing voltages of  $V_d=1$  V and  $V_g=0.5$  V. The  $V_T$  is derived from the measured  $I_d$  in transistor saturation and subthreshold regions for the low and high  $V_T$  states, respectively, and the variations of  $V_T$  are shown as a function of time in Figure 4. The fluctuation ranges of the  $V_T$  during the five day test are less than 0.25 V in both the high and low  $V_T$  states, indicating the reasonable nonvolatile nature of the FCTs.

To test the repeatability of the configuration, gate configuration-voltage pulses with a duration of 1 ms and magnitudes  $V_{\rm g}=7$  and -5 V were applied alternately to configure the FCTs to the "high" and "low"  $I_{\rm d}$  states, respectively, and reading pulses with a duration of 1 ms and magnitude  $V_{\rm g}=1$  V were then applied to read the state of the device. The FCTs were configured reversibly and repeatedly for more than  $\sim 3 \times 10^5$  cycles with an on/off ratio of the drain—current about 1 order of magnitude before the measured device failed, probably due to a breakdown of the insulating gate SiO<sub>2</sub> layer.

The device configuration speeds were determined by varying the duration of the  $V_{\rm g}$  pulse. A larger pulse amplitude was required in order to configure the FCTs effectively with a shorter pulse duration. The FCTs were successfully configured by pulses with a duration of 1  $\mu$ s and an amplitude of 20 V. Any further decrease of the pulse duration would require a further increase of the pulse amplitude, which would likely induce electrical breakdown of the thin gate SiO<sub>2</sub> layer. Optimization of the gate structure should improve the configuration speed.

To understand the mechanism of the FCT configuration process, a two-terminal test device with the same Al/Ti/RbAg<sub>4</sub>I<sub>5</sub>/MEH-PPV/SiO<sub>2</sub>/p-Si structure as the FCT gate shown in the Figure 1a was constructed and the change of the chemical composition in such test devices was investi-

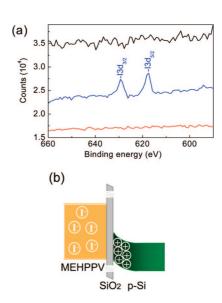

**Figure 5.** (a) XPS spectra of the I 3d region from the  $SiO_2$  surfaces after the separation of the MEH-PPV/SiO<sub>2</sub> interface from the test devices configured by a positive gate bias of +4 V (red), a negative gate bias of -4 V (blue), and without configuration (black). (b) An energy band diagram of the MEH-PPV,  $SiO_2$ , and p-Si channel layers with iodide ions (marked as  $I^-$ ) injected into the MEH-PPV layer and holes (marked as +) accumulated at the  $SiO_2/p$ -Si interface.

gated by X-ray photoelectron spectroscopy (XPS). The test devices used regular p-Si wafers with a boron dopant concentration of  $\sim$ 5  $\times$  10<sup>15</sup>/cm<sup>3</sup> instead of the SOI wafers for the FCT devices and had a large area of  $\sim 3 \text{ mm}^2$  defined by its top metal electrode deposited through a shadow mask. A thick Al layer was deposited on the backside of the p-Si wafer as the bottom electric contact. The test devices were configured by applying positive or negative bias across the two electrodes. The chemical depth profile in the test devices was initially examined with XPS by ion-milling the multiple layers from the top electrode, but the difficulty to precisely control the ion-milling through the stacks of drastically different materials prevented the measurement of the depth profile. Utilizing a new procedure, the Al/Ti/RbAg<sub>4</sub>I<sub>5</sub>/MEH-PPV top layers were glued to a glass slide and then physically peeled off from the substrate to expose the SiO<sub>2</sub>/p-Si surfaces, which were subsequently analyzed by XPS. As shown in Figure 5a, the presence of the I 3d<sub>3/2</sub> and I 3d<sub>5/2</sub> peaks of iodide anions in the XPS spectrum from the test device configured by applying a gate voltage of -4 V for 100 s clearly indicates that iodide anions were injected into the organic layer and driven all the way to the MEH-PPV/SiO<sub>2</sub> interface by the gate electric field. No iodine peaks were observed for the exposed SiO<sub>2</sub> surfaces for either devices without configuration or after applying a positive configuration voltage of 4 V for 100 s.

On the basis of the electronic measurements and the XPS results, we propose the following FCT configuration mechanism based on the electric field-driven modulation of iodide ions in the FCT gate region. When a large negative gate voltage  $|V_g - (V_d + V_s)/2| > 1.5$  V is applied to the Al/Ti gate electrode, Ag cations in the RbAg<sub>4</sub>I<sub>5</sub> ionic conductive layer are reduced, while iodide anions are injected from the

RbAg<sub>4</sub>I<sub>5</sub> layer into the MEH-PPV polymer layer.<sup>17,18</sup> The iodide anions in the MEH-PPV layer drift toward the MEH-PPV/SiO<sub>2</sub> interface in the high electric field. The progressive increase of the anionic concentration near the MEH-PPV/ SiO<sub>2</sub> interface induces the accumulation of holes in the p-type Si channel, resulting in the increase of the gate threshold voltage  $V_{\rm T}$  of the FCT (Figure 5b). When a positive gate voltage  $|V_g - (V_d + V_s)/2| > 1.5 \text{ V}$  is applied, the opposite process occurs, resulting in the decrease of  $V_T$ . During the configuration process, the RbAg<sub>4</sub>I<sub>5</sub> ionic conductive layer functions as a source or sink of iodide anions for the MEH-PPV layer. When the FCT is operated as a FET with  $|V_g|$  $(V_{\rm d} + V_{\rm s})/2$  < 1.5, the electrochemical processes are below threshold and the configured device state is nonvolatile. Compared with the configuration of electronic charge by electron tunneling in a floating gate FET, the configuration of the ionic charge in the FCT utilizes configuration voltages with much lower amplitude, 12 which enables the FCT to be configured more controllably, flexibly, and conveniently by modifying the number and amplitude of the configuration voltage pulses compatible with CMOS circuits. The conventional logic function of a floating gate FET has to be interrupted by the configuration process, but a FCT can be configured while functioning as a conventional FET. The simple double-layer gate structure of the FCT can also be conveniently integrated with different self-assembled nanowires. The analog configurability and plasticity of the FCT can potentially be used to correct variations of device characteristics and defects and provide defect tolerance in nanoscale integrated circuits.8-11 Moreover, a circuit composed of dynamic field-configurable transistors can, in principle, be configured to arbitrary functions from external signals, 19 which may yield a synaptic electronic circuit with learning capability.

In summary, an organic/Si hybrid field-configurable transistor (FCT) has been fabricated on a Si nanowire FET platform. The gate threshold voltage of the FCT was configured to analog values ranging between -1 V and +4 V precisely, dynamically, repeatedly, and reversibly by adjusting the amplitude, polarity, and duration of a configuration gate voltage pulse  $V_{\rm g}$  with  $|V_{\rm g}-(V_{\rm d}+V_{\rm s})/2| > 1.5$  V. The FCT is nonvolatile and can operate as a conventional Si FET as long as  $|V_{\rm g}-(V_{\rm d}+V_{\rm s})/2| < 1.5$  V. We are exploring the fabrication and demonstration of a defect-

tolerant nanoelectronic circuit and a synaptic electronic circuit with dynamic learning functions based on FCTs.

**Acknowledgment.** This work was supported in part by DARPA and by the California NanoSystems Institute (CNSI).

**Supporting Information Available:** Closed-loop feed-back circuit for targeted configuration; characteristics of a Si field effect transistor as control. This material is available free of charge via the Internet at http://pubs.acs.org.

## References

- The International Technology Roadmap for Semiconductors: http:// www.itrs.net/.

- (2) Cui, Y.; Zhong, Z. H.; Wang, D. L.; Wang, W. U.; Lieber, C. M. Nano Lett. 2003, 3, 149–152.

- (3) Tans, S. J.; Verschueren, A. R. M.; Dekker, C. Nature 1998, 393, 49–52.

- (4) Chen, Y.; Ohlberg, D. A. A.; Li, X. M.; Stewart, D. R.; Williams, R. S.; Jeppesen, J. O.; Nielsen, K. A.; Stoddart, J. F.; Olynick, D. L.; Anderson, E. Appl. Phys. Lett. 2003, 82, 1610–1612.

- (5) Huang, Y.; Duan, X. F.; Wei, Q. Q.; Lieber, C. M. Science 2001, 291, 630–633.

- (6) Derycke, V.; Martel, R.; Appenzeller, J.; Avouris, P. Nano Lett. 2001, 1, 453–456.

- (7) Chen, Y.; Jung, G. Y.; Ohlberg, D. A. A.; Li, X. M.; Stewart, D. R.; Jeppesen, J. O.; Nielsen, K. A.; Stoddart, J. F.; Williams, R. S. *Nanotechnology* **2003**, *14*, 462–468.

- (8) Heath, J. R.; Kuekes, P. J.; Snider, G. S.; Williams, R. S. Science 1998, 280, 1716–1721.

- (9) Goldstein, S.; Budiu, M.; Mishra, M.; Venkataramani, G. Reconfigurable Computing and Electronic Nanotechnology. In *Proceedings of the IEEE International Conference on Application-Specific Systems, Architectures, and Processors, 2003*; IEEE: New York, 2003; pp 132–142.

- (10) Strukov, D. B.; Likharev, K. K. J. Nanosci. Nanotechnol. 2007, 7, 151–167.

- (11) Snider, G. S.; Williams, R. S. Nanotechnology 2007, 18, 035204.

- (12) Diorio, C.; Hasler, P.; Minch, A.; Mead, C. A. IEEE Trans. Electron Devices 1996, 43, 1972–1980.

- (13) Li, Q. L.; Surthi, S.; Mathur, G.; Gowda, S.; Zhao, Q.; Sorenson, T. A.; Tenent, R. C.; Muthukumaran, K.; Lindsey, J. S.; Misra, V. Appl. Phys. Lett. 2004, 85, 1829–1831.

- (14) Duan, X. F.; Huang, Y.; Lieber, C. M. Nano Lett. 2002, 2, 487-490.

- (15) Li, C.; Fan, W. D.; Lei, B.; Zhang, D. H.; Han, S.; Tang, T.; Liu, X. L.; Liu, Z. Q.; Asano, S.; Meyyappan, M.; Han, J.; Zhou, C. W. Appl. Phys. Lett. 2004, 84, 1949–1951.

- (16) Geller, S. Science 1967, 157, 310.

- (17) Lai, Q. X.; Zhu, Z. H.; Chen, Y.; Patil, S.; Wudl, F. Appl. Phys. Lett. 2006, 88, 133515.

- (18) Patil, S.; Lai, Q. X.; Marchioni, F.; Jung, M. Y.; Zhu, Z. H.; Chen, Y.; Wudl, F. J. Mater. Chem. 2006, 16, 4160–4164.

- (19) Funahashi, K. Neural Networks 1989, 2, 183–192.

NL073112Y